Digital Packet/DCC Extended Packet

DCC Extended Packet Formats

For more information see NMRA Standard S-9.2.1. This article references the May 15 2022 version. Read the standard for more detailed information, as this is an overview, the standard will be considered as correct in case of disagreement.

The NMRA Communications Standard for Digital Communications (S-9.2) provides a minimal, basic packet format required for interoperability. Extended Packet Formats provide the framework to enable realistic operations to occur.

These formats adhere to the packet format as defined in S-9.2. While the baseline packet has a length of 3 data bytes separated by a "0" bit, a packet using the extended packet format definition may have a length of between 3 and 6 data bytes each separated by a "0" bit.

This document is meant to provide information on Extended Packet Formats. For in-depth information consult the most recent version of NMRA Standard S-9.9.1.

Terminology

- Accessory Decoder: DCC Decoder used for control/animation of stationary devices

- Broadcast Command: Using address 00000000, the command is sent and available to all decoders

- Consist: Two or more multifunction decoders responding to the same commands [1]

- Multifunction Decoder: DCC Decoder used for vehicle operation, which controls multiple functions such as speed, direction, lighting effects or sound

- Mobile Decoder: Another term for Multifunction Decoder

- Vehicle: A model railroad device such as a locomotive, also includes rolling stock

Format Definitions

In this article, following the template of S-9.2.1, bits within the address and data bytes will be defined using the following abbreviations. Individual bytes within a specific packet format are separated by spaces. Bytes which are within square [ ] brackets can occur one or more times as necessary. Bytes are separated by a 0. The last byte is a XOR error detection byte followed by a 1. Bits are numbered right to left with bit 0 (the right most bit) being the least significant bit (LSB) and bit 7 (the left most bit) being the most significant bit (MSB).

| Data Bit Defintions | |

|---|---|

| A | Address Bit |

| 0 | Bit which has a value of 0 |

| 1 | Bit which has a value of 1 |

| U | Undefined bit, 0 or 1 are valid states |

| B | Bit position / Address |

| C | Instruction Type field |

| G | Instruction Sub Type |

| T | Instruction Tertiary Type |

| F | Flag, determines Instruction Implementation |

| L | Low Order Binary State Control Address |

| H | High Order Binary State Control Address |

| S | Sub Address of decoder |

| V | CV Address bit |

| D | Data |

| X | Signal Head aspect bit |

| E | Error detection bit |

Address Partitions

The first data bytes is the address byte, which contains the primary address. To allow for different types of Decoder, the range of addresses is partitioned as follows:

| Address Partitioning | |

|---|---|

| Address | |

| 0 | Broadcast Address |

| 1-127 (Inclusive) | Multifunction Decoder Primary Address |

| 128-191 (Inclusive) | Basic Accessory Decoder 9 Bit address, Extended Accessory Decoder 11 bit address |

| 192-231 (Inclusive) | Multifunction Decoder Extended Address |

| 232-252 (Inclusive) | Reserved for Future Use |

| 253-254 (Inclusive) | Advanced Extended Packet Formats |

| 255 | Idle Packet |

Broadcast Command (Multifunction Decoders)

Format: {preamble} 0 00000000 0 {instruction-bytes} 0 EEEEEEEE 1

Instructions send to the broadcast address must be obeyed. The instruction byte may be up to three bytes in length.

Instruction Packet (Multifunction Decoders)

Primary Address:

{preamble} 0 [ AAAAAAAA ] 0 {instruction-bytes} 0 EEEEEEEE 1

Extended Address:

{preamble} 0 [ AAAAAAAA ] 0 [ AAAAAAAA ] 0 {instruction-bytes} 0 EEEEEEEE 1

- The most significant bit of the address data is bit 5 of the first byte (Bit 5 is underlined).

- The primary address byte is 8 bits long. If the most significant bits are between decimal 192 and 231 (inclusive) a second address byte must immediately follow, with an additional 8 bits of address data.

- Instruction bytes are data bytes used to transmit commands to the decoder.

| Instruction Bytes | ||||

|---|---|---|---|---|

| CCCDDDD | 0 | or | ||

| CCCDDDD | 0 | DDDDDDDD | or | |

| CCCDDDD | 0 | DDDDDDDD | 0 | DDDDDDDD |

Each instruction field consists of a three-bit instruction field and a 5-bit data field. Some 5-bit data fields can also contain Instruction Subtypes, Instruction Tertiary types or Flags.

- CCCDDDDD can also equal CCCGGGGG or CCCGTTTT

| Instruction Type | |

|---|---|

| 000 | Decoder and Consist Control |

| 001 | Advanced Operation Instructions |

| 010 | Speed and Direction Instruction (Reverse) |

| 011 | Speed and Direction Instruction (Forward) |

| 100 | Function Group One Instructions |

| 101 | Function Group Two Instructions |

| 110 | Feature Expansion |

| 111 | CV Access Instruction |

| Tertiary-Type Instructions (TTT) | |

|---|---|

| 000 | F=0, Factory Reset, F=1, Hard Reset |

| 001 | Factory Test |

| 010 | Reserved |

| 011 | |

| 100 | |

| 101 | Set Advanced Addressing |

| 110 | Reserved |

| 111 | F=1 Decoder Acknowledgment Request |

Decoder Control (CCCG=0000)

This allows set up or modification of decoder configuration

The instruction byte can be 0000TTTF, with or without a following data byte. This allows specified features to be set, dependant on the value of the flag (F).

Advanced Operations (CCC=001)

For this instruction the instruction bytes = 001GGGGG 0 DDDDDDDD

Set Advanced Addressing

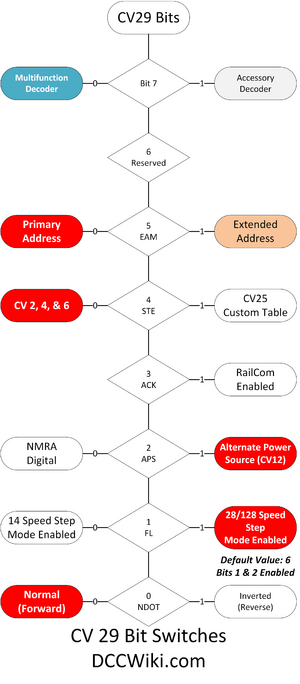

This command selects either the Primary (7-bit) or Extended (14 bit) addressing mode, depending on the state of CV29.

Consist Control

- Main article: Digital_Packet#Decoder_and_Consist_Control

This instruction controls consist creation and activation/deactivation.

When this is in effect, only speed and direction commands acted on are those sent to the consist address.

Functions will still respond when addressed to the decoder's base address. They will also respond to the consist address if the appropriate bits in CV21 and 22 are set.

128 Speed Steps

An instruction of 11111 is used to send one of 129 decoder speed steps. A single byte following defines speed and direction, Bit 7 determines Direction while Bits 0-6 indicate speed.

Speed and Direction

Two instructions, formatted as follows: [2]

Reverse {Instruction Bytes} 010DDDDD

Forward {Instruction Bytes} 011DDDDD

Data bits 0 – 3 (underlined) are used for speed. Bit Four is bolded.

- If Bit 1 (FL) of CV29 is 1, Bit 4 is an intermediate speed step[3]

- If Bit 1 (FL) of CV29 is 0, Bit 4 is used to control FL

CV29 controls whether 14 or 28/128 mode is in use.

Function Group Instructions

There are two possible instructions

Group One {Instruction Bytes} 100DDDDD [4]

Group Two {Instruction Bytes} 101DDDDD [4]

Up to 5 auxiliary functions (FL, F1-F4) can be controlled by Function Group One. [5]

Function Group Two offers eight additional functions (F5-F12).

Feature Expansion Instruction

The instructions in this group provide for support of additional features within decoders. [6]

- Features include

- Date & Time

- System Time

Function Control for

- F-13-F20

- F21-F28

- F29-36

- F37-f44

- F45-52

- 53-60

- 61-68

There are 23 sub-instructions which are reserved. [7]

Configuration Variable Access Instruction (CCC=111)

The purpose of this instruction is setup or modification of configuration variables, using either the programming track or on the main line.

This instruction can be in two forms:

- Short form for modifying selected frequently modified CVs

- Long form for verification or modification or any selected CV

Only a single CV access instruction can be contained within the packet.

Configuration Variable Access Instruction - Short Form

| GGGG | Description | CVs Affected | Two Identical Packets Required |

|---|---|---|---|

| 0000 | Not Available | ||

| 0010 | Acceleration Adjustment Value | CV23 | No |

| 0011 | Deceleration Adjustment Value | CV24 | No |

| 0100 | Exteneded Address | CV17, CV18, CV29 | Yes |

| 0101 | Indexed CVs | CV31 | CV32 |

| 1001 | See S-9.2.3 Appendix B |

The remaining values of GGGG are reserved. [7] Paired CVs must be written at the same time to avoid problems. If the decoder successfully receives both packets, it shall respond with an operations mode acknowledgment.

This explains why some CV changes are often prevented when using Operations Mode programming.

Configuration Variable Access Instruction - Long Form

The long form allows the direct manipulation of all CVs. [8]

This instruction is valid for both Primary and Extended Addresses. The decoder shall not act on an instruction send to its consist address. The format is as follows:

{instruction bytes}= 1110GGVV 0 VVVVVVVV 0 DDDDDDDD

- GG=00, Reserved

- GG=01, Verify Byte

- GG=11, Write Byte

- GG=10, Bit Manipulation

Verify Byte

This instruction compares the selected CV to the data byte.

Write Byte

This instruction writes the data to the CV. Two identical packets ar need for this operation. [9]

Bit Manipulation

This works in much the same manner as Verify and Write, acting on a single bit.

Accessory Digital Decoder Packet Formats

Accessory Decoders have both a Basic and Extended Accessory Control Packet Format. Broadcast Commands are also supported.

Operations Mode Acknowledgment

The operations-mode acknowledgment mechanism defined in S-9.3.2 are the only valid acknowledgement in operations mode. Whenever an acknowledgment is requested, the decoder shall respond using this mechanism described in S-9.3.2

References

- ↑ See S-9.2.2 CV19 for more details

- ↑ S-9.2.1, 2.3.3

- ↑ If the speed step mode is mismatched between the command station and multifunction decoder, the headlight will toggle on and off as the throttle is changed.

- ↑ 4.0 4.1 Any function in this group may be directionally qualified

- ↑ If Bit 1 of CV29 has a value of one (1), then bit 4 controls function FL, otherwise bit 4 has no meaning.

- ↑ See TN-3-05

- ↑ 7.0 7.1 The NMRA shall not issue a NMRA Conformance Warrant for any product that uses any instruction or sub-instruction that has been reserved by the NMRA

- ↑ Because of the length of this instruction, care must be taken to ensure that the maximum time between packets is not exceeded.

- ↑ See S-9.2.2 for more information on paired CVs.